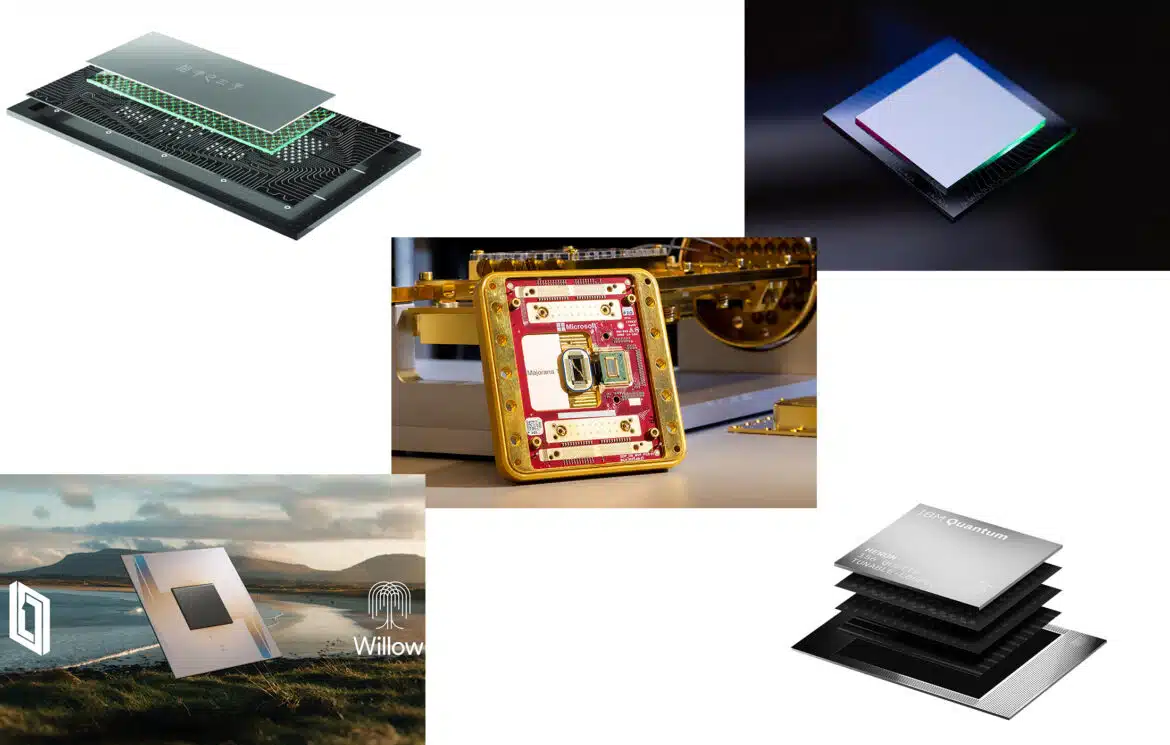

A corrida em direção à computação quântica tolerante a falhas: AWS Ocelot, Microsoft Majorana 1, Google Willow, IBM Heron R2 e Zuchongzhi 3.0

Introdução

A computação quântica está entrando em uma nova fase marcada por cinco grandes anúncios de cinco potências quânticas — Zuchongzhi , Amazon Web Services (AWS) , Microsoft , Google e IBM — todos nos últimos 4 meses. Esses são apenas anúncios alimentados por exagero ou marcam um progresso real em direção à computação quântica útil, em larga escala e tolerante a falhas — e talvez sinalizem um cronograma acelerado para o “ Q-Day ”? Pessoalmente, estou otimista sobre esses anúncios. Cada um deles revela uma estratégia diferente e interessante para enfrentar o maior desafio do campo: a correção quântica de erros . A inovação combinada impulsiona o campo para a frente de uma maneira grande. Mas vamos nos aprofundar em alguns detalhes:

- Ontem, a potência da computação quântica da China, as equipes de pesquisa Zuchongzhi, revelaram o Zuchongzhi 3.0 , um novo processador quântico supercondutor com 105 qubits.

- Poucos dias atrás, a AWS revelou o “Ocelot”, um protótipo de chip quântico construído em torno de qubits de gato bosônicos com correção de erros em seu próprio design.

- Poucos dias antes, a Microsoft apresentou o “Majorana 1” (com grande repercussão na mídia, devo dizer), reivindicando o primeiro processador quântico usando qubits topológicos que prometem estabilidade inerente contra ruído.

- Em dezembro passado, o Google anunciou seu chip “Willow” , que leva qubits transmon supercondutores a uma fidelidade sem precedentes, demonstrando pela primeira vez que adicionar qubits pode reduzir as taxas de erro exponencialmente (um limite fundamental para tolerância a falhas).

- E em novembro do ano passado, a IBM anunciou o chip quântico “Heron R2” atualizado, que avança de forma semelhante a arquitetura de qubit supercondutor com mais qubits, acopladores ajustáveis e mitigação de fontes de ruído, permitindo que circuitos com milhares de operações funcionem de forma confiável.

Esses desenvolvimentos são significativos porque abordam diretamente o obstáculo dos erros quânticos que limitou o progresso dos computadores quânticos. E eles fazem isso de maneiras diferentes. Ao melhorar a estabilidade do qubit e a correção de erros, eles estão coletivamente empurrando a indústria para mais perto da computação quântica prática, em larga escala e tolerante a falhas. Na corrida em direção a um computador quântico útil, o progresso é medido não apenas na contagem de qubits, mas na superação de problemas de ruído e escala — e é exatamente isso que esses anúncios visam.

Igualmente importante, essas descobertas ilustram abordagens diversas e complementares. Os qubits bosônicos da AWS visam reduzir a sobrecarga de correção de erros codificando informações em estados de osciladores. Os qubits topológicos da Microsoft buscam aproveitar estados exóticos da matéria para proteger intrinsecamente informações quânticas no nível de hardware. Google e IBM, embora ambos continuem com circuitos supercondutores, estão melhorando drasticamente a coerência e usando engenharia inteligente (códigos de superfície no caso do Google e acopladores ajustáveis e otimizações de software no caso da IBM) para avançar em direção à operação tolerante a falhas. Zuchongzhi está ao mesmo tempo demonstrando as melhorias que podem ser alcançadas por melhor redução de ruído no design do circuito e melhor empacotamento de qubit.

Cada desenvolvimento é crítico à sua maneira. Juntos, eles representam um empurrão concertado em direção ao objetivo há muito buscado de um computador quântico prático – um que possa manter a coerência quântica por tempo suficiente, e em uma escala grande o suficiente, para resolver problemas reais além do alcance das máquinas clássicas.

Análise de cada anúncio

AWS Ocelot: Qubits Bosonic Cat e correção de erros integrada

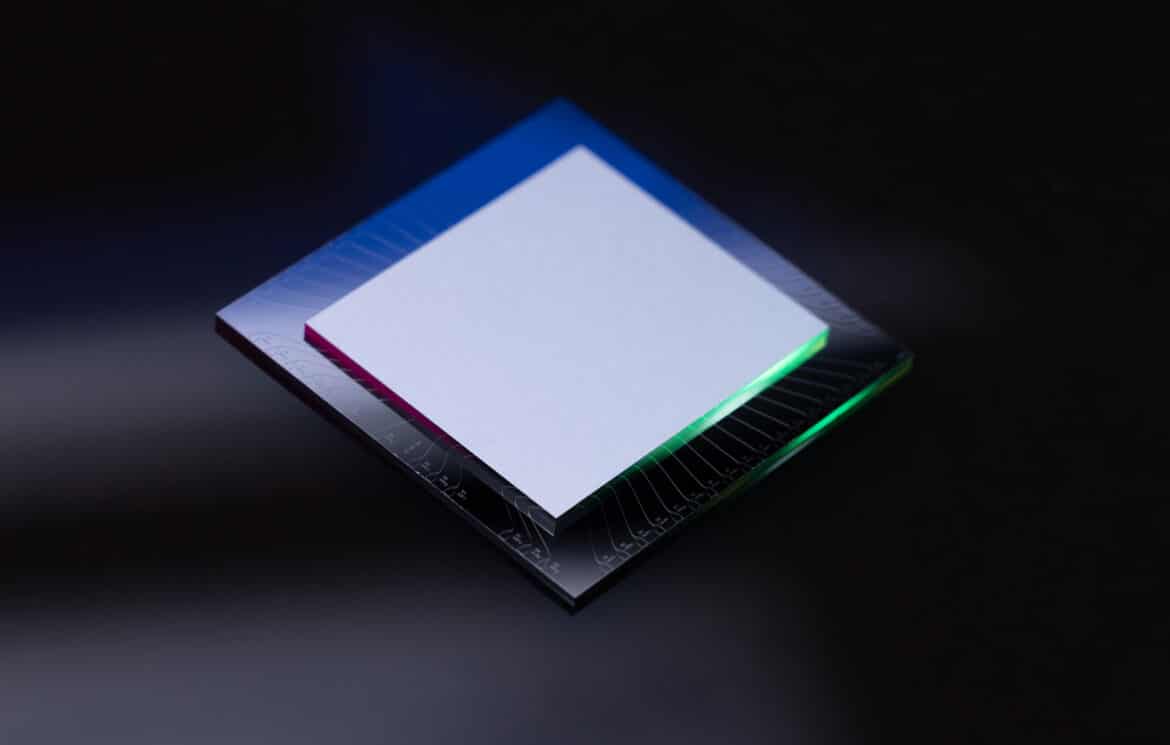

O anúncio da AWS do processador quântico Ocelot marca uma mudança de paradigma no design de hardware ao tornar a correção de erros quânticos um recurso primário do chip, em vez de uma reflexão tardia . Ocelot é um protótipo que consiste em dois chips de silício empilhados (cada um com ~1 cm²) com circuitos supercondutores fabricados em suas superfícies. Ele integra 14 componentes principais: cinco qubits de dados bosônicos “cat”, cinco circuitos de buffer não lineares para estabilizar esses estados cat e quatro qubits auxiliares para detectar erros. O termo qubit cat se refere a um qubit codificado em uma superposição quântica de dois estados coerentes de um oscilador harmônico (análogo ao famoso experimento mental de gato vivo/morto de Schrödinger). Cada qubit cat é realizado em um ressonador de micro-ondas (oscilador) de alta qualidade feito de tântalo supercondutor, projetado para ter estados de vida extremamente longa. A principal vantagem é que esses qubits exibem um forte viés de ruído: erros de inversão de bits (ou seja, inversões entre os dois estados coerentes do oscilador) são suprimidos exponencialmente aumentando o número de fótons no oscilador. Na verdade, a AWS relata tempos de erro de inversão de bits se aproximando de um segundo – mais de 1.000× mais longo do que a vida útil de um qubit supercondutor normal. Isso deixa o modo de erro primário restante como inversões de fase (erros de fase relativos entre os estados de base do cat), que ocorrem na ordem de dezenas de microssegundos. Ao reduzir drasticamente um tipo de erro no nível físico, o Ocelot pode concentrar recursos na correção do outro.

Para capturar e corrigir erros de inversão de fase, o Ocelot usa um código de repetição simples nos cinco qubits cat. Os qubits cat são organizados em uma matriz linear e emaranhados por meio de portas CNOT especialmente ajustadas com os quatro qubits ancilla transmon, que atuam como detectores de síndrome para erros de fase. Em essência, uma inversão de fase em qualquer qubit cat é detectada por meio de medições de verificação de paridade (habilitadas por essas ancillas), e as informações são codificadas redundantemente para que um único erro de fase possa ser identificado e corrigido (muito parecido com um código de repetição clássico que corrigiria uma inversão de bit). Enquanto isso, o circuito de buffer conectado a cada qubit cat e o design com viés de ruído das portas CNOT garantem que o processo de detecção de erros não introduza muitos erros de inversão de bit em troca. Essa concatenação de um código bosônico (para reduzir inversões de bit) com um código clássico simples (para corrigir inversões de fase) é o que a AWS chama de arquitetura de correção de erros com eficiência de hardware. Notavelmente, todo o qubit lógico (código de repetição de distância-5) no Ocelot usa apenas 5 qubits de dados + 4 ancillas = 9 qubits físicos no total, em comparação com 49 qubits físicos que um código de superfície de distância-5 padrão exigiria. O artigo da Nature da AWS relata que mudar de um código mais curto (distância 3) para o código de distância-5 completo reduziu significativamente a taxa de erro lógico (especialmente para inversões de fase) sem ser prejudicado por erros de inversão de bits adicionais. Na verdade, o erro lógico total por ciclo foi de aproximadamente 1,65% para o código de 5 qubits, essencialmente o mesmo que ~1,72% para o código de 3 qubits. Isso demonstra que o Ocelot manteve um grande viés em favor de erros de fase – a redundância adicionada suprimiu inversões de fase mais rápido do que qualquer nova oportunidade de inversão de bits poderia prejudicá-lo. Em termos práticos, Ocelot alcançou uma memória lógica totalmente corrigida de erros que abrange cinco qubits físicos, com uma taxa de erro líquida muito menor do que qualquer qubit individual.

Embora o Ocelot seja apenas um protótipo de qubit lógico, suas especificações são impressionantes. O Tbit-flip (tempo de vida do bit-flip) dos cat qubits é de ~1 s e o Tphase-flip de ~20 µs. Em comparação, um qubit transmon típico pode ter T1 e T2 na faixa de 0,02–0,1 ms (20–100 µs). Assim, os qubits do Ocelot são ordens de magnitude mais robustos contra bit-flips. A desvantagem é que os erros de fase permanecem frequentes, mas é exatamente isso que o código de repetição lida.

Um potencial desafio de escala para essa abordagem será implementar portas lógicas entre várias unidades lógicas cat-qubit – até agora, o Ocelot demonstra um qubit de memória (ele armazena um estado quântico com fidelidade aprimorada), mas não uma porta lógica entre dois qubits lógicos. Estender o esquema para um computador totalmente programável exigirá vincular muitos desses qubits codificados e orquestrar medições complexas de síndrome, tudo isso preservando o delicado viés de ruído. Isso exigirá maior integração (mais ressonadores, acopladores e circuitos de leitura) e provavelmente novas técnicas para gerenciar estados de número de fótons mais altos em muitos modos. Além disso, embora os códigos de repetição sejam simples, códigos de correção de erros mais poderosos (com maior distância) podem ser necessários para operações lógicas, o que pode aumentar a sobrecarga. A AWS, no entanto, está otimista – eles observam que, se essa abordagem bosônica for escalonada, um computador quântico totalmente tolerante a falhas pode precisar de apenas um décimo do número de qubits físicos que as arquiteturas convencionais exigiriam. O sucesso do Ocelot é uma prova de conceito de que qubits bosônicos podem ser integrados a um chip e superar qubits lógicos equivalentes baseados em transmon, potencialmente acelerando o cronograma para um computador quântico útil em vários anos.

Para mais informações, veja: AWS ataca o Quantum Stage com o chip Ocelot para qubits ultraconfiáveis .

Majorana 1 da Microsoft: Qubits topológicos e a busca por qubits estáveis

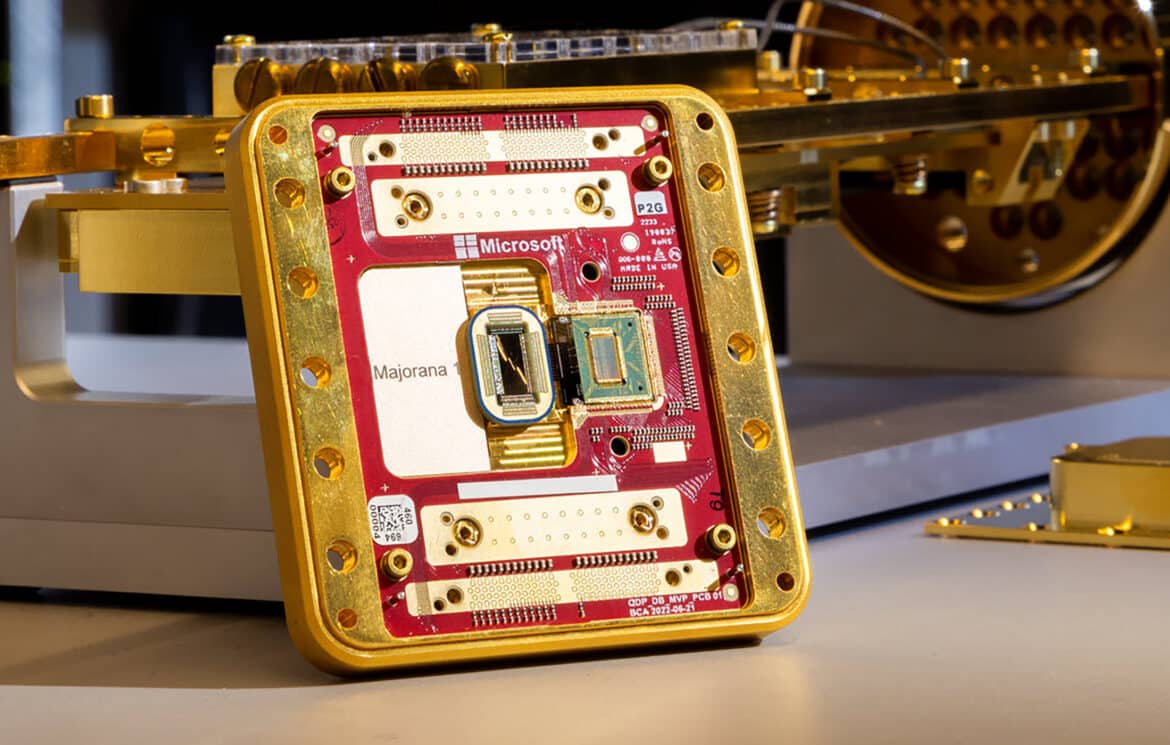

O chip Majorana 1 da Microsoft representa um avanço muito aguardado na computação quântica topológica. É o primeiro protótipo de processador quântico baseado em modos zero Majorana (MZMs) – quasipartículas exóticas que emergem nas extremidades de nanofios especialmente projetados e que se comportam como quasipartículas que são suas próprias antipartículas. Em teoria, pares desses MZMs podem codificar informações quânticas de uma forma não local que é inerentemente protegida de muitas formas de ruído. O chip Majorana 1 é um dispositivo do tamanho da palma da mão que abriga oito qubits topológicos em um único chip, fabricado com uma nova pilha de materiais de semicondutor de arsenieto de índio (InAs) e supercondutor de alumínio. Esses materiais formam o que a Microsoft chama de “topocondutores”, criando um estado supercondutor topológico quando resfriado e colocado em um campo magnético. Nesse estado, cada minúsculo nanofio (na ordem de 100 µm de comprimento) pode hospedar um par de modos zero Majorana em suas extremidades. Quatro MZMs (por exemplo, as extremidades de dois nanofios) juntos codificam o estado de um qubit de forma distribuída – essencialmente armazenando informações quânticas na paridade de elétrons compartilhados entre as extremidades do fio, em vez de em qualquer local único. Espera-se que essa codificação topológica seja altamente resistente a perturbações locais: um erro exigiria uma mudança global que alterasse a topologia (por exemplo, quebrando o par ou movendo um Majorana de uma extremidade para a outra), o que é energeticamente ou estatisticamente muito improvável. Como resultado, um qubit codificado em MZMs deve permanecer coerente por muito mais tempo do que um qubit convencional, sem correção de erro ativa – pelo menos para certos tipos de erros (notavelmente, inversões de bits na base protegida topologicamente).

Ao anunciar Majorana 1, a Microsoft revelou que, após quase duas décadas de pesquisa (!), eles finalmente conseguiram a criação e detecção de modos zero de Majorana em um dispositivo que permite operações de qubit. Os oito qubits do chip são organizados de uma forma que é projetada para ser escalável para milhões de qubits em um chip. Cada qubit é extremamente pequeno (cerca de 1/100 de milímetro, ou ~10 µm, em tamanho) e rápido de manipular por meio de controles eletrônicos. Uma das principais conquistas na publicação Nature que o acompanha foi uma demonstração de uma medição de paridade interferométrica de disparo único dos modos Majorana. Em termos mais simples, eles podem ler o estado conjunto de um par de MZMs (que revela o valor do qubit) de uma só vez, sem precisar fazer a média de muitas tentativas. Isso é crucial para usá-los como qubits. As descobertas revisadas por pares do artigo da Nature confirmam que a Microsoft criou as condições para os modos Majorana e mediu suas informações quânticas de forma confiável. No entanto, vale a pena notar uma ressalva importante: embora a Microsoft tenha anunciado a criação de um qubit topológico, os revisores da Nature incluíram um comentário de que os resultados “ não representam evidências da presença de modos zero de Majorana ” em si, mas demonstram uma arquitetura de dispositivo que poderia hospedá-los. Em outras palavras, a comunidade científica está cautelosa – eles querem uma prova mais definitiva de que o comportamento observado é realmente devido a MZMs. Para mais sobre essa controvérsia e outras controvérsias passadas com a equipe Majorana da Microsoft, veja meu artigo: Chip quântico baseado em Majorana da Microsoft – além do hype .

De uma perspectiva teórica, um qubit topológico estável é como o Santo Graal do hardware quântico. Suas implicações são profundas. Primeiro, a estabilidade por design poderia reduzir drasticamente a sobrecarga necessária para correção de erros – você pode não precisar executar constantemente medições de síndrome ou ter dezenas de qubits físicos protegendo um bit lógico, se o qubit físico já for extremamente imune a ruído. A Microsoft prevê escalar qubits Majorana de forma que um único chip possa hospedar na ordem de 1.000.000 de qubits. Eles argumentam que somente com tal escala massiva (habilitada pelo pequeno tamanho e controlabilidade digital de qubits topológicos) os computadores quânticos atingirão a complexidade para aplicações transformadoras. Um milhão de qubits topológicos, se cada um for muito mais confiável do que os qubits de hoje, poderia teoricamente executar os trilhões de operações necessárias para algoritmos úteis como quebrar moléculas complexas ou fatorar grandes números.

É preocupante, no entanto, que atualmente Majorana 1 tenha apenas oito qubits, e mesmo esses ainda não foram mostrados executando portas lógicas quânticas arbitrárias – o anúncio focou na inicialização e medição (controle de paridade) dos qubits. Os próximos passos provavelmente envolverão demonstrar operações de qubit como trançamento (troca de Majoranas para executar portas lógicas) e interações de dois qubits, e mostrar que essas operações obedecem às propriedades topológicas esperadas (por exemplo, certas portas sendo inerentemente tolerantes a falhas). Se qualquer uma dessas peças falhar – por exemplo, se fatores ambientais como envenenamento de quasipartículas perturbarem os MZMs com muita frequência – correção de erro adicional ainda seria necessária além da proteção topológica. A Microsoft reconheceu que nem todas as portas são protegidas topologicamente; por exemplo, a chamada porta T (uma operação não Clifford) ainda seria “barulhenta” e exigiria técnicas suplementares. Em resumo, Majorana 1 é uma aposta ousada em uma abordagem fundamentalmente diferente para a computação quântica. Após anos de contratempos e ceticismo, os últimos resultados da Microsoft começaram a convencer a comunidade de que os qubits topológicos podem finalmente ser reais. Se a alegação for válida, é um momento decisivo: um novo estado da matéria (supercondutor topológico) aproveitado para criar qubits que são naturalmente resilientes. Isso pode eventualmente se traduzir em processadores quânticos com desempenho efetivo muito maior, à medida que a sobrecarga de correção de erros é reduzida. No curto prazo, Majorana 1 será usado internamente para pesquisas futuras — ainda não está resolvendo nenhum problema útil — mas estabelece uma base teórica que pode ultrapassar outras tecnologias se for dimensionada conforme o esperado.

Para mais informações, veja: Chip quântico baseado em Majorana da Microsoft – além do hype .

Google Willow: Um processador Transmon de 105 qubits que atinge limites de correção de erros

O chip quântico Willow do Google é o mais recente na linha de processadores supercondutores da equipe de IA quântica do Google e vem com duas grandes conquistas:

- aumenta significativamente a coerência e a fidelidade, de modo que adicionar mais qubits diminui a taxa geral de erros (cruzando o cobiçado limite de correção de erros) e

- demonstrou uma computação de altíssima complexidade em minutos que levaria um tempo astronomicamente longo para um supercomputador clássico.

Willow contém 105 qubits supercondutores da variedade transmon , dispostos em uma rede 2D adequada para o esquema de correção de erros de código de superfície. Os qubits são conectados por acopladores em um layout semelhante ao processador Sycamore de 54 qubits anterior do Google, mas com melhorias arquitetônicas notáveis. Uma atualização importante é que Willow retém a sintonia de frequência de qubits/acopladores (como Sycamore tinha) para interações flexíveis, ao mesmo tempo em que melhora drasticamente os tempos de coerência: o tempo médio de relaxamento de energia do qubit T1 em Willow é de cerca de 68 µs, comparado a ~20 µs em Sycamore. Essa melhoria de ~3× na coerência se deve em parte a melhores materiais e fabricação (o Google cita um novo design de qubit e mitigação de fontes de ruído) e em parte devido a técnicas de calibração aprimoradas (aproveitando o aprendizado de máquina e eletrônicos de controle mais eficientes). Em conjunto, as fidelidades de gate de dois qubits foram aproximadamente dobradas em comparação com a geração Sycamore. Se os gates CZ de Sycamore tiveram taxas de erro na ordem de 0,6%, os de Willow estão em torno de ~0,3% ou melhor (gates de qubit único têm fidelidade ainda maior). Esses números colocam Willow no regime dos melhores qubits supercondutores relatados em qualquer laboratório até o momento.

Crucialmente, esse aumento de hardware permitiu que o Google demonstrasse a correção de erro quântico escalável pela primeira vez. Usando o código de superfície (um código topológico de correção de erro quântico em uma grade 2D de qubits), a equipe codificou um qubit lógico em tamanhos crescentes de código: um patch 3×3 de qubits (código de distância 3), um patch 5×5 (distância 5) e um patch 7×7 (distância 7). Com cada aumento na distância do código, eles observaram uma supressão exponencial das taxas de erro – especificamente, cada passo acima reduziu a taxa de erro lógico em cerca de um fator de 2 (o erro lógico de um código 7×7 foi ~4× menor do que o de um código 3×3). Pelo maior código (49 qubits físicos codificando 1 qubit lógico), a vida útil do qubit lógico excedeu a do melhor qubit físico individual no chip. Isso significa que o qubit lógico é, na verdade, de qualidade superior a qualquer qubit físico puro — um marco conhecido como correção de erro quântico “além do ponto de equilíbrio”. Na linguagem da correção de erros, o Google cruzou o limite de tolerância a falhas: suas operações estão em um regime “abaixo do limite”, onde adicionar mais qubits ao código produz menos erros líquidos. Esta é a primeira vez que um sistema quântico supercondutor mostrou definitivamente esse comportamento em tempo real (tentativas anteriores não viram nenhuma melhoria no tamanho do código ou apenas uma melhoria marginal). Para obter informações mais detalhadas sobre a conquista da correção de erros do Google, consulte o artigo da Nature que acompanha o anúncio: Correção de erro quântico abaixo do limite do código de superfície . Conseguir isso exigiu não apenas qubits excelentes, mas também decodificação e feedback em tempo real. O Google implementou ciclos rápidos de extração de síndrome de erro e algoritmos de decodificação (com a ajuda de algoritmos de computação clássica e ML personalizados) que podem identificar e corrigir erros em tempo real, mais rápido do que eles se acumulam. No artigo da Nature publicado junto com Willow, eles relatam que com o código 7×7, a probabilidade de erro lógico por ciclo foi cortada pela metade em comparação com o código 5×5, estabelecendo firmemente que eles estão operando no regime escalável. Em resumo, o Google Willow é a primeira plataforma onde a correção de erro quântico “funciona” na prática – alcançando o ponto em que maior realmente significa melhor em termos de matrizes de qubit.

Outra manchete do anúncio do Google foi uma demonstração de poder computacional bruto. Willow executou um benchmark de amostragem de circuito aleatório de tamanho sem precedentes, completando-o em cerca de 4,5 minutos. O Google afirma que o supercomputador Frontier (atualmente o mais rápido do mundo, com ~1,35 exaflops) levaria cerca de 10 25 anos para executar a tarefa equivalente. Essa separação massiva (quântica vs clássica) excede em muito a demonstração de “supremacia quântica” de 2019, onde a tarefa foi estimada em 10.000 anos em um supercomputador IBM. Na verdade, após otimizações, essa tarefa de 2019 foi reduzida para uma questão de dias em máquinas clássicas, mas o Google observa que para esse novo experimento, mesmo contabilizando futuras melhorias clássicas, a aceleração quântica está crescendo ” a uma taxa exponencial dupla ” conforme o tamanho do circuito aumenta. O benchmark envolveu emaranhar todos os 105 qubits em um padrão complexo e executar muitas camadas de portas aleatórias de dois qubits, um teste que é computacionalmente difícil para simulação clássica e leva o chip quântico aos seus limites. A capacidade de executar um circuito tão grande (mais de 5.000 operações de porta de dois qubits no total) foi habilitada pelas taxas de erro mais baixas do Willow e pela capacidade de correção de erros – de fato, a IBM havia executado um circuito similarmente grande (2.880 portas de dois qubits) em 2023 em seu Eagle de 127 qubits, mas exigiu uma mitigação pesada de erros para obter um resultado válido. O marco do Google indica que a supremacia quântica foi reafirmada em uma escala maior, e agora com uma máquina que está mais perto de ser corrigida por erros. É uma prova de que o aumento da contagem de qubits mais a redução de erros podem produzir resultados computacionais muito além do alcance clássico, reforçando a confiança de que o aumento de escala desbloqueará uma vantagem quântica útil.

Do ponto de vista arquitetônico, Willow não introduz novos tipos radicais de qubits — ainda é um chip transmon — mas mostra avanços incrementais que se fundem em um grande salto. As melhorias de coerência (68 µs T1, ~50–70 µs T2) vieram de atualizações de materiais como melhor substrato e tratamento de superfície e possivelmente usando bump-bonds de índio (embora não confirmado) para reduzir perdas. Os acopladores e qubits ajustáveis permitem flexibilidade no isolamento de qubits quando ociosos e na redução de diafonia (uma técnica que a IBM também emprega em seus chips), o que contribui para menores taxas de erro. Além disso, o Google empregou software de controle avançado: calibrações automatizadas, aprendizado de máquina para ajuste fino de pulsos e um agente de aprendizado por reforço para otimizar o desempenho da correção de erros. A integração de todas essas peças é o que permitiu que Willow atingisse o regime abaixo do limite. Um desafio à frente para o Google é como continuar dimensionando a contagem de qubits enquanto mantém os erros baixos. O roteiro deles, como outros, exigirá modularidade – possivelmente conectando vários chips de mais de 100 qubits ou desenvolvendo wafers maiores – já que simplesmente dobrar qubits em um dado poderia reintroduzir ruído e dificuldades de fabricação. Mas a abordagem de código de superfície agora foi validada: se cada módulo puder ter, digamos, 1000 qubits com uma taxa de erro de 0,1%, pode-se começar a montar qubits lógicos de altíssima qualidade usando qubits físicos suficientes. A conquista do Google com Willow fornece uma meta quantitativa clara: um qubit lógico com erro de ~10 -3 (0,1%) por operação foi alcançado com 49 qubits; empurrar esse erro para baixo para, digamos, 10 -6 exigirá talvez algumas centenas de qubits físicos por qubit lógico. Willow é o trampolim que demonstra que a curva de escala se mantém conforme o esperado.

Em suma, o anúncio do Willow do Google é uma forte validação do caminho transmon/surface-code para tolerância a falhas: ele mostrou que com hardware aprimorado e codificação inteligente, agora é possível suprimir erros exponencialmente com o tamanho do sistema. Isso move o campo para mais perto da correção de erros quânticos prática e, junto com isso, mais perto de executar algoritmos úteis de forma confiável em uma máquina quântica.

Para mais informações, veja meu resumo do anúncio: Google anuncia o chip Willow Quantum .

IBM Heron R2: Arquitetura de acoplador ajustável e volume quântico aprimorado

O anúncio da IBM do processador Heron R2 é uma evolução de seu hardware quântico supercondutor focado em aumentar a contagem de qubits, mantendo alto desempenho. O Heron R2 contém 156 qubits organizados na topologia de rede hexagonal pesada exclusiva da IBM. Este é um gráfico de conectividade de qubit onde cada qubit se conecta a no máximo 3 vizinhos em um padrão hexagonal com conexões ausentes, que a IBM usa para reduzir a diafonia e habilitar códigos de correção de erros eficientes. A família Heron é notável por introduzir acopladores ajustáveis entre cada par de qubits conectados, um recurso visto pela primeira vez no Heron R1 (um chip de 133 qubits estreou no final de 2023). No R2, a IBM aumentou a contagem de qubits para 156 estendendo a rede e incorporando lições das melhorias de entrega de sinal do sistema Osprey de 433 qubits. O design do acoplador ajustável permite que a interação de dois qubits seja ligada ou desligada (e ajustada em força) dinamicamente, o que suprime bastante o acoplamento indesejado e as colisões de frequência quando várias operações estão acontecendo em paralelo. Isso efetivamente elimina muitos erros de “diafonia” que assolam as arquiteturas de acoplamento fixo. De acordo com a IBM, a Heron demonstrou uma melhoria de 3 a 5 vezes nas métricas de desempenho do dispositivo em comparação com sua geração anterior (a Eagle de 127 qubits), ao mesmo tempo em que “praticamente eliminava” a diafonia. Números específicos do Heron r1 (133 qubits) mostraram um volume quântico (QV) de 512 – uma medida que combina o número de qubits e a fidelidade do gate – que era um novo recorde para a IBM naquela época. O Heron R2 provavelmente leva isso ainda mais longe.

O chip Heron R2 também introduziu uma nova técnica de mitigação de “sistema de dois níveis” (TLS) em hardware. Defeitos de TLS nos materiais (como flutuadores microscópicos de dois níveis em superfícies ou interfaces) são uma causa conhecida de decoerência de qubit e erros esporádicos. A IBM construiu circuitos ou procedimentos de calibração no Heron R2 para detectar e mitigar o impacto do ruído TLS nos qubits. O resultado é uma estabilidade aprimorada das frequências de qubit e, por extensão, melhores tempos de fidelidade e coerência de gate. Embora a IBM não tenha citado publicamente a média T1/T2 para o Heron R2, sua ênfase na mitigação de TLS sugere que a coerência de cada qubit está mais consistentemente próxima dos limites superiores (potencialmente várias centenas de microssegundos). Eles também melhoraram os processos de leitura e redefinição (a IBM vem desenvolvendo leitura de qubit rápida e de alta fidelidade e reutilização de qubit via redefinição para acelerar os circuitos). Em termos de integração com software, o Heron R2 é entregue via Quantum Cloud da IBM e é totalmente compatível com melhorias de tempo de execução do Qiskit . Na verdade, a IBM destacou que, ao combinar o hardware Heron R2 com avanços de software como circuitos dinâmicos e compilação paramétrica, eles alcançaram um desempenho sustentado de 150.000 operações de camada de circuito por segundo (CLOPS) neste sistema. Este é um aumento dramático na velocidade de execução do circuito – em comparação, em 2022 seus sistemas executaram ~1k CLOPS, e no início de 2024 cerca de 37k CLOPS. CLOPS mais rápidos significam que os pesquisadores podem executar algoritmos mais profundos e complexos dentro do tempo de coerência dos qubits ou reunir mais estatísticas em menos tempo de relógio de parede.

A evidência mais concreta do avanço do Heron R2 foi o anúncio da IBM de que ele pode executar circuitos quânticos de forma confiável com até 5.000 portas de dois qubits. Isso é quase o dobro das 2.880 portas de dois qubits usadas no experimento de “utilidade quântica” de 2023 da IBM no chip Eagle. Nesse experimento (publicado na Nature), a IBM mostrou que um circuito complexo de muitos qubits poderia ser executado com fidelidade suficiente – usando mitigação de erros – para obter um resultado significativo além do alcance da simulação clássica de força bruta. Agora, com o Heron R2, circuitos quase duas vezes mais longos podem ser executados com precisão sem ajustes de hardware personalizados, usando a cadeia de ferramentas Qiskit padrão. Em outras palavras, o Heron R2 empurrou os processadores quânticos da IBM firmemente para o regime de “escala de utilidade”, onde eles podem explorar algoritmos que não são modelos de brinquedo. É importante ressaltar que essa capacidade de 5.000 portas foi alcançada por meio de melhorias de hardware (menores taxas de erro por porta) e mitigação de erros de software. A IBM menciona um “algoritmo de mitigação de erro tensor (TEM)” no Qiskit que foi aplicado. TEM é um método para reduzir erros em saídas de circuitos por meio de pós-processamento clássico e conhecimento do ruído, que a IBM integrou em seu tempo de execução. Então, o Heron R2, pareado com tais técnicas, pode executar circuitos longos 50× mais rápido do que era possível um ano antes, e com precisão suficiente para que as saídas sejam confiáveis.

Em termos de métricas brutas: o erro mediano de gate de dois qubits da IBM no Heron R2 não é explicitamente declarado no anúncio, mas dado o desempenho, é provável que seja da ordem de ~0,5% ou melhor, com alguns qubits atingindo fidelidade de 99,5–99,7%. Gates de qubit único geralmente estão acima de 99,9%. A topologia hexadecimal pesada tem um pouco menos de conectividade do que uma grade completa, mas tem uma vantagem para o código de superfície (que a IBM usa em alguns experimentos) porque forma naturalmente uma grade planar de dados e mede qubits quando dispostos adequadamente. A IBM vem testando códigos de superfície de pequena distância em chips anteriores e provavelmente fará o mesmo no Heron também. No entanto, a estratégia de curto prazo da IBM também enfatizou a mitigação de erros e a “utilidade quântica” em vez da correção completa de erros, o que significa que eles tentam encontrar maneiras de obter resultados úteis do hardware em mãos combinando-o com o processamento clássico. O Heron R2 é uma continuação dessa filosofia: melhorar o hardware apenas o suficiente para expandir os limites do que pode ser feito na era NISQ, enquanto estabelece as bases para um hardware verdadeiramente tolerante a falhas no futuro. A arquitetura Heron (com acopladores ajustáveis) é, de fato, o modelo para os próximos sistemas maiores e modulares da IBM. A IBM planeja conectar vários chips Heron por meio de interconexões flexíveis e um acoplador especial (codinome Flamingo) para escalar para processadores efetivos maiores. Eles já demonstraram um protótipo dessa abordagem modular, mostrando que dois chips Heron poderiam ser vinculados a um portão de emaranhamento em uma distância de ~metro com apenas uma pequena perda. Portanto, o Heron R2 não é apenas um dispositivo autônomo de 156 qubits, mas também um módulo na arquitetura de computador quântico System Two da IBM, que prevê a combinação de módulos para atingir milhares de qubits. Em resumo, o anúncio do Heron R2 da IBM é sobre refinamento e integração: mais qubits, melhor controle de ruído (acopladores ajustáveis + mitigação de TLS) e software mais rápido, tudo isso junto. O resultado é um processador quântico que amplia significativamente a capacidade da IBM de executar algoritmos complexos (aproximando-se do desafio de profundidade de qubit de 100×100 que eles representavam). Embora possa não ostentar um tipo de qubit fundamentalmente novo ou um avanço físico dramático, é um passo incremental crítico. Ele mostra que a IBM pode aumentar a escala sem sacrificar o desempenho, o que é essencial na marcha em direção a uma máquina tolerante a falhas.

Zuchongzhi 3.0: Avanço da China em Hardware Quântico Supercondutor

Pesquisadores chineses revelaram oficialmente o Zuchongzhi 3.0, um processador quântico supercondutor de 105 qubits que estabelece um novo padrão em velocidade e escala computacionais. Em sua demonstração de estreia, o chip executou uma tarefa de amostragem de circuito aleatório de 83 qubits (32 camadas de profundidade) em apenas alguns minutos, produzindo resultados que levariam um supercomputador clássico de última geração da ordem de 6,4 bilhões de anos para simular. Isso representa uma aceleração estimada de 10 15 vezes sobre a computação clássica e uma melhoria de aproximadamente um milhão de vezes (6 ordens de magnitude) sobre o experimento Sycamore anterior do Google. O feito, publicado como um artigo de capa na Physical Review Letters , reforça o avanço da China na corrida pela vantagem computacional quântica, marcando a vantagem quântica mais forte alcançada até o momento em uma plataforma supercondutora.

O Zuchongzhi 3.0 apresenta atualizações significativas em relação ao seu antecessor de 66 qubits. O novo processador integra 105 qubits transmon em uma grade bidimensional com 182 acopladores (interconexões) para permitir padrões de emaranhamento mais complexos. Ele ostenta um tempo de coerência médio mais longo de cerca de 72 µs e operações de alta fidelidade (aproximadamente 99,9% para portas de qubit único e 99,6% para portas de dois qubits) – conquistas possibilitadas por melhorias de engenharia, como redução de ruído no design do circuito e melhor empacotamento de qubits. Essas inovações técnicas permitem que o Zuchongzhi 3.0 execute circuitos quânticos mais profundos do que os chips anteriores e até mesmo suporte experimentos iniciais de correção de erros quânticos. A equipe demonstrou elementos de memória de código de superfície (código de distância 7) neste chip e está trabalhando para atingir limites de correção de erros mais altos, destacando os novos recursos habilitados pela estabilidade e escala aprimoradas do processador.

Comparação técnica expandida

Cada uma dessas cinco abordagens de computação quântica traz algo único para a mesa. Nesta seção, tentarei comparar suas métricas técnicas e como elas contribuem para o objetivo abrangente da computação quântica tolerante a falhas.

Tipo e arquitetura de qubit

Os cinco processadores quânticos empregam três tecnologias distintas de qubit.

AWS Jaguatirica

O AWS Ocelot usa cat qubits supercondutores, onde cada qubit é codificado em dois estados coerentes de um ressonador de micro-ondas. Este design suprime intrinsecamente certos erros ao polarizá-los (erros de inversão de bits são fortemente suprimidos). O chip do Ocelot integra 14 componentes principais: 5 ressonadores cat-qubit servindo como qubits de dados, 5 circuitos de buffer para estabilizar esses qubits osciladores e 4 qubits ancilla supercondutores para detectar erros nos qubits de dados. Notavelmente, é uma arquitetura de qubit lógico eficiente em hardware: apenas 9 qubits físicos produzem um qubit lógico protegido graças ao viés de erro integrado do cat qubit. O chip é fabricado com processos de microeletrônica padrão (usando tântalo em ressonadores de silício) para escalabilidade. Em essência, a AWS pegou um circuito baseado em transmon e o ampliou com qubits osciladores bosônicos para criar uma memória quântica com preservação de viés.

Microsoft Majorana-1

Em contraste, o Microsoft Majorana-1 usa uma abordagem totalmente diferente: qubits topológicos baseados em modos zero de Majorana (MZMs). Esses qubits são realizados em um “supercondutor topológico” especial formado em nanofios de arsenieto de índio/alumínio em temperaturas criogênicas. Cada qubit (um chamado tetron) consiste em um par de nanofios hospedando quatro MZMs no total (dois MZMs por fio, nas extremidades). As informações quânticas são armazenadas não localmente na paridade de ocupação de elétrons entre dois MZMs, o que as torna inerentemente protegidas do ruído local. Os qubits Majorana são manipulados por meio de operações de trança ou esquemas baseados em medição equivalentes, em vez dos pulsos de porta usados para transmons. Majorana-1 é um protótipo de 8 qubits (o que significa que pode hospedar 8 qubits topológicos) implementado como uma matriz 2D desses dispositivos baseados em nanofios. É o primeiro processador a demonstrar essa arquitetura Topological Core, que a Microsoft afirma poder ser dimensionada para milhões de qubits em um chip se a abordagem for comprovada. O desafio de ler o estado de um qubit topológico (já que a informação está “escondida” em uma paridade) é resolvido por um novo mecanismo de medição: acoplar as extremidades do nanofio a um pequeno ponto quântico e sondar com micro-ondas. A reflexão do sinal de micro-ondas muda dependendo se a paridade do qubit é par ou ímpar, permitindo a leitura única do estado do qubit Majorana.

Os três chips restantes – Google Willow , IBM Heron R2 e Zuchongzhi 3.0 – usam qubits transmon supercondutores, mas com arquiteturas de circuito diferentes.

Google Salgueiro

O Willow do Google é um processador supercondutor de 105 qubits que se baseia no design Sycamore anterior do Google. Os qubits são dispostos em uma grade plana 2D com acopladores ajustáveis ou acoplamentos capacitivos fixos formando uma topologia de vizinho mais próximo. A rede do Willow é efetivamente uma grade retangular densa (matriz 15×7) semelhante a uma rede quadrada pesada, com uma coordenação média de ~3,5 acoplamentos por qubit. (Cada qubit interage com 3 ou 4 vizinhos, facilitando portas de dois qubits em paralelo.) O Google otimizou o design do Willow para alta conectividade e baixa diafonia – por exemplo, usando uma porta de dois qubits semelhante ao iSWAP que pode ser aplicada em muitos pares simultaneamente sem interferência excessiva. O chip Willow é fabricado em um processo multicamadas com circuitos de alumínio supercondutores em silício e inclui ressonadores de micro-ondas integrados para leitura de cada qubit.

IBM Heron R2

O IBM Heron R2 também é um processador transmon supercondutor, mas a IBM emprega sua arquitetura de rede hexagonal pesada exclusiva. O Heron R2 contém 156 qubits transmon dispostos de forma que cada qubit tenha no máximo 3 vizinhos (uma rede hexagonal pesada). Essa geometria deliberadamente “poda” a conectividade em relação a uma grade quadrada para reduzir a diafonia e os erros correlacionados. Crucialmente, o Heron usa elementos de acoplador ajustáveis entre qubits. Esses acopladores (com base em circuitos de junção Josephson adicionais) podem ser ativados para mediar interações de dois qubits ou desativados para isolar efetivamente os qubits quando nenhuma porta é pretendida. Essa arquitetura de acoplamento ajustável suprime drasticamente interações indesejadas e diafonia durante períodos ociosos. A primeira revisão do Heron R1 tinha 133 qubits; o Heron R2 revisado expandiu para 156 qubits na mesma arquitetura. Cada qubit é acoplado a um ressonador dedicado para leitura de estado, e o chip apresenta entrega avançada de sinal (fiação e encapsulamento flexíveis de alta densidade) para controlar tantos qubits em paralelo. O design da IBM enfatiza a modularidade: chips Heron de 156 qubits são os blocos de construção para sistemas maiores, e vários chips Heron podem ser conectados por meio de links de micro-ondas no Quantum System Two da IBM para escalar além de um único dado.

USTC Zuchongzhi 3.0

O Zuchongzhi 3.0, desenvolvido pela USTC na China, também consiste em qubits transmon supercondutores em uma matriz planar. Ele tem 105 qubits dispostos em uma rede retangular 2D (15 linhas × 7 colunas). Ao contrário do hexadecimal pesado da IBM, o Zuchongzhi usa uma conectividade relativamente alta: cada qubit é acoplado a até 4 vizinhos mais próximos (exceto nas bordas), semelhante à abordagem do Google. Na verdade, o dispositivo é conhecido por ser bastante semelhante ao Willow do Google em termos de contagem de qubits e conectividade. Um aspecto distinto da arquitetura do Zuchongzhi 3.0 é sua integração flip-chip: ele é construído a partir de dois chips de safira unidos. Um chip contém os 105 qubits transmon e 182 circuitos de acoplamento (os acopladores no plano entre os qubits), e um segundo chip é montado no topo contendo toda a fiação de controle e ressonadores de leitura. Essa integração 3D separa as interconexões de controle densas do plano de qubit, reduzindo a interferência e permitindo um layout de qubit mais compacto. Os transmons são implementados usando fabricação de tântalo/alumínio supercondutor (a USTC introduziu material de tântalo para melhorar os fatores de qualidade). O uso de flip-chip e novos materiais no Zuchongzhi 3.0 mostra um forte foco de engenharia em aumentar a contagem de qubit supercondutor sem sacrificar a coerência.

Resumo dos tipos e arquiteturas de Qubit

Ocelot e Majorana-1 buscam designs radicais de qubit (bosônico e topológico, respectivamente) para incorporar resiliência de erro no nível de hardware, enquanto Willow, Heron R2 e Zuchongzhi 3.0 refinam a abordagem transmon bem estabelecida com layout inteligente e inovações de acoplamento. Os chips baseados em transmon reúnem as maiores contagens de qubit (105–156 qubits) e demonstraram benchmarks de circuitos complexos, enquanto os dispositivos cat-qubit e Majorana, embora menores em número de qubit, representam saltos de prova de conceito em direção a arquiteturas tolerantes a falhas construídas em física inovadora.

Tempos de Coerência (T1 e T2)

O tempo de coerência é uma métrica crítica para o desempenho do qubit, pois determina por quanto tempo um qubit pode reter informações quânticas. Existem duas escalas de tempo relevantes: T1, o tempo de relaxamento de energia (por quanto tempo o qubit permanece em um estado excitado antes de decair para o solo) e T2, o tempo de defasagem (por quanto tempo a coerência de fase de superposição é mantida). Em um qubit ideal de dois níveis, a população de estados excitados decai comoe−para/E1, e elementos fora da diagonal da matriz de densidade do qubit decaem comoe−para/E2. T1 e T2 mais longos são melhores, permitindo que mais operações sejam realizadas antes que erros ocorram. Os cinco chips mostram diferenças significativas em coerência, em grande parte decorrentes de suas diferentes implementações de qubit:

AWS Jaguatirica

A arquitetura do qubit cat atinge uma assimetria extrema em tempos de coerência. Ao codificar o qubit em um par de estados osciladores, os qubits de Ocelot exibem um tempo de erro de inversão de bits (T1) excedendo 10 segundos em demonstrações experimentais – várias ordens de magnitude mais longo do que os transmons comuns. Em outras palavras, transições espontâneas entre os estados lógicos |0⟩ e |1⟩ (que correspondem a dois estados coerentes distintos do ressonador) são extraordinariamente raras. Este T1 de 10+ s para inversões de bits é 4–5 ordens maior do que os qubits cat anteriores e muito maior do que qualquer T1 transmon. No entanto, isso tem um custo: a coerência de inversão de fase (T2) do qubit cat é muito mais curta, porque o ambiente pode causar mais facilmente a defasagem entre os dois estados de base cat. O tempo de inversão de fase relatado é da ordem de 5×10−7s (sub-microsegundo) em experimentos atuais de qubits de gato. Em essência, os qubits de Ocelot têm um ruído altamente enviesado: processos de inversão de bits são suprimidos por ~10 7 em relação à inversão de fase. Os circuitos de buffer em Ocelot são projetados para prolongar um pouco a coerência de fase, mas T2 ainda é muito mais curto que T1. Isso é aceitável, pois o sistema usará correção de erro ativa para lidar com erros de fase. O ponto-chave é que os qubits de Ocelot raramente perdem energia (T1 ~ 10 s), mas perdem a coerência de fase relativamente rápido, o que significa que suas superposições precisam de estabilização periódica.

Microsoft Majorana-1

Espera-se que os qubits Majorana sejam intrinsecamente duradouros porque os estados dos qubits são armazenados não localmente. No dispositivo Majorana-1 inicial, a equipe relatou que perturbações externas (por exemplo, eventos de envenenamento de quasipartículas que invertem a paridade) são raras: aproximadamente uma inversão de paridade por milissegundo em média. Podemos tratar isso como um T1 efetivo na ordem de 1 ms para o qubit topológico, o que significa que a probabilidade de um qubit mudar espontaneamente de estado é de cerca de10−3por milissegundo. Isso já é uma ordem de magnitude de vida útil maior do que os qubits supercondutores típicos. Isso implica, por exemplo, que durante uma operação de 1 µs, a chance de um erro induzido pelo ambiente é da ordem de10−6, que é muito baixo. Quanto ao T2, um qubit codificado topologicamente deve ser amplamente imune a muitos mecanismos de defasagem, já que perturbações de fase locais não alteram o estado de paridade global. O T2 prático pode ser limitado pelo acoplamento residual entre os modos Majorana ou flutuações no ajuste do dispositivo (por exemplo, ruído de campo magnético), mas valores quantitativos não foram totalmente divulgados. Os qubits Majorana demonstraram a capacidade de manter a superposição quântica sem decaimento em escalas de tempo experimentais mais curtas do que a vida útil da paridade de 1 ms, indicando T2 na ordem de pelo menos centenas de microssegundos no dispositivo atual. Em essência, Majorana-1 mostra coerência em escala de milissegundos — um salto significativo — graças à proteção topológica. (As primeiras medições tiveram ~1% de erro de leitura, o que é mais uma infidelidade de leitura do que um limite de coerência, e a equipe vê caminhos para reduzir ainda mais esse erro.)

Google Salgueiro

Willow representa uma grande melhoria na coerência em relação ao chip Sycamore anterior do Google. O Google relata tempos de coerência médios de T1 ≈ 98 µs e T2 (CPMG) ≈ 89 µs para os qubits no Willow. Isso é um aumento de cerca de 5× em relação à coerência de ~20 µs do Sycamore. Essa melhoria foi alcançada por meio de mudanças de materiais e design (por exemplo, usando fabricação aprimorada para reduzir defeitos do sistema de dois níveis e melhor blindagem para reduzir ruído). Um T1 de 98 µs significa que um qubit excitado perde energia com uma constante de tempo de quase 0,1 ms, e T2 de 89 µs indica que a coerência de fase é mantida quase pelo mesmo tempo. Esses números estão entre os mais altos relatados para chips supercondutores de grande escala. Crucialmente, a coerência de Willow é uniforme em seus 105 qubits – as médias implicam que a maioria dos qubits está nessa faixa, o que é importante para operações multi-qubit. Com coerência de ~100 µs e tempos de porta na ordem de dezenas de nanossegundos, os qubits de Willow podem sofrer na ordem de103operações antes da descoerência (na ausência de correção de erros). Essa longa coerência foi essencial para permitir que Willow executasse circuitos relativamente profundos e até mesmo experimentos de correção de erros com sucesso. Vale a pena notar que o Google empregou desacoplamento dinâmico e sequências CPMG (daí citar T2,CPMG) para estender o T2 efetivo para ~89 µs. O T2 verdadeiro (defasagem de Ramsey sem ecos) pode ser menor, mas por meio de técnicas de eco eles mitigam a defasagem não homogênea.

IBM Heron R2

A família Heron da IBM também alcançou tempos de coerência substanciais, embora a IBM frequentemente enfatize outras métricas (como fidelidade de gate) sobre T1/T2 bruto em divulgações públicas. O design heavy-hex e a introdução de uma camada de mitigação TLS no R2 visavam especificamente melhorar a coerência em todo o chip de 156 qubits. Ao reduzir defeitos do sistema de dois níveis e perdas de material, a IBM provavelmente tem muitos qubits com T1 na ordem de 100 µs ou mais. Em dispositivos IBM anteriores (por exemplo, chips Falcon de 27 qubits), T1 ~ 50–100 µs e T2 ~ 50 µs eram típicos. O Heron R2, sendo uma nova revisão, provavelmente empurrou o T1 ainda mais. De fato, uma fonte observa que as melhorias na fidelidade de gate de dois qubits do Heron vieram em parte de melhor coerência e estabilidade em todo o chip devido ao controle do ambiente TLS. Sem números oficiais da IBM neste texto, extrapolamos: a coerência do Heron R2 deve ser comparável ao alcance do Willow. O foco da IBM na uniformidade significa que não há qubits outliers com T1 muito baixo – eles projetam para um piso estável de desempenho. É razoável supor que T1, T2 no Heron estão em poucos × 101 Intervalo de µs (dezenas de microssegundos). A IBM relatou qubits individuais com T1 > 300 µs no passado, mas para a grande matriz da Heron, uma estimativa mais segura é T1 ~100 µs, T2 ~100 µs em média. Isso é apoiado pela introdução pela IBM de novas técnicas de filtragem e isolamento que “ melhoram a coerência e a estabilidade em todo o chip ”. Em resumo, os transmons do Heron R2 têm alta, mas talvez um pouco menor coerência do que o melhor do Willow (a IBM prioriza a redução de ruído e diafonia de outras maneiras também). O layout hexadecimal pesado em si ajuda na coerência ao minimizar o congestionamento de frequência e a interferência. Portanto, os tempos de coerência da IBM estão no mesmo patamar do Google – na ordem de10−4 s – garantindo que centenas a milhares de operações possam ser executadas por qubit antes da decoerência se a mitigação de erros for aplicada.

USTC Zuchongzhi 3.0

A equipe da USTC fez do aprimoramento da coerência uma meta importante no Zuchongzhi 3.0, e eles alcançaram uma melhoria marcante em relação ao seu chip anterior de 66 qubits. Eles relatam uma média de T1 ≈ 72 µs e T2 (CPMG) ≈ 58 µs nos 105 qubits. Esses valores, embora ligeiramente abaixo do Google Willow, ainda são muito altos para um dispositivo grande (para comparação, o Zuchongzhi 2.0 teve coerência significativamente menor, embora números exatos não tenham sido fornecidos neste snippet). A equipe credita várias estratégias de engenharia para essa melhoria: ajuste das geometrias do capacitor qubit para reduzir a perda dielétrica da superfície, atenuação criogênica aprimorada para cortar o ruído ambiental (aumentando o T2) e uso da fabricação de tântalo/alumínio para obter melhor qualidade do material. Eles também implementaram um processo de colagem de colisão de índio (flip-chip) que reduziu os contaminantes da interface e melhorou o T1 ao atenuar o efeito Purcell e outros canais de perda. Os resultados falam de um ato de equilíbrio cuidadoso: após adicionar mais qubits e acopladores, eles ainda aumentaram a coerência média (T1 ~72 µs) em relação à geração anterior. No entanto, como mostra a comparação publicada, o T1/T2 do Zuchongzhi 3.0, embora excelente, é um pouco menor que o do Willow (98/89 µs) – provavelmente devido à integração ligeiramente mais densa ou às diferenças de materiais. Ainda assim, com coerência de ~60–70 µs, os qubits do Zuchongzhi podem lidar com muitas operações dentro de sua janela de coerência. A equipe descobriu que esse aumento de coerência se traduziu diretamente em erros de gate mais baixos (as taxas de erro de qubit único e de dois qubits caíram de acordo).

Resumo dos Tempos de Coerência

Majorana-1 e Ocelot oferecem novas formas de coerência estendida: qubits Majorana com estabilidade de paridade de ~1 ms e qubits cat com um espantoso T1 de ~10 s (mas T2 curto). Os chips baseados em transmon (Willow, Heron R2, Zuchongzhi 3.0) todos alcançam T1,T2 na ordem de10−5para10−4segundos (dezenas de microssegundos a quase 0,1 ms), o que é o estado da arte para qubits supercondutores em sua escala. Esses tempos de coerência são longos o suficiente para que, se combinados com correção de erro quântico, erros de qubit possam ser significativamente suprimidos. De uma perspectiva matemática, se uma operação de porta levaparage um qubit temE2, o erro de decoerência por porta é aproximadamente1–experiência(−parag/E2)≈parag/E2paraparag≪E2. Por exemplo, o tempo de porta de dois qubits de Willow de ~42 ns em um qubit comµE2≈89µeproduz um erro de defasagem intrínseco ~µ42ns/89microssegundos≈5×10−4, consistente com seu erro medido de dois qubits na ordem de10−3(já que erros de controle e T1 contribuem com pequenos erros adicionais). Cada plataforma levou a coerência a um regime suficiente para experimentos multi-qubit complexos: as plataformas supercondutoras fazem isso com materiais e design aprimorados, enquanto as plataformas cat e topológicas fazem isso por meio de codificações de qubit fundamentalmente diferentes que eliminam ou adiam certos canais de decaimento.

Taxas de erro e técnicas de correção de erros

Como as computações quânticas são tão sensíveis a erros, todas essas plataformas empregam estratégias para minimizar e corrigir erros no nível físico ou lógico. Nós distinguimos taxas de erro físico (erros por porta ou por tempo em qubits individuais) de taxas de erro lógico (erros em qubits codificados que usam muitos qubits físicos com um código de correção de erros). Um conceito-chave é o limite de tolerância a falhas: se as taxas de erro físico puderem ser empurradas abaixo de algum limite (em torno de 1% para muitos códigos como o código de superfície), então aumentar o tamanho do código suprimirá exponencialmente a taxa de erro lógico. Cada um dos cinco chips aborda esse desafio de forma diferente.

AWS Jaguatirica

Ocelot ataca o problema do erro enviesando o ruído do qubit para que um tipo de erro seja extremamente raro. Nos qubits cat do Ocelot, os erros de inversão de bits (erros X) são essencialmente eliminados no nível do hardware (tempo de inversão de bits ~10 s, conforme observado). Isso significa que a taxa de erro físico para inversões de bits é astronomicamente baixa (na ordem de10−8por segundo ou menos). Os erros dominantes restantes são inversões de fase (erros Z), que ocorrem com probabilidade muito maior (tempo de coerência de fase ~0,5 µs). No entanto, erros de fase podem ser detectados e corrigidos por um código mais simples, já que inversões de bits não ocorrem para agravar o problema. Ocelot essencialmente constrói correção de erro quântico na arquitetura qubit desde o início. Os 5 qubits cat mais 4 ancillas no chip implementam um pequeno código de correção de erro quântico que estabiliza continuamente o qubit lógico. Embora a AWS não tenha detalhado publicamente o código exato, é provável que seja um código de repetição ou código de verificação de paridade entre os qubits cat que detecta inversões de fase. O resultado é um qubit lógico com eficiência de hardware: a AWS obteve um qubit lógico de apenas 9 qubits físicos, em comparação com os milhares de qubits físicos que um código de superfície exigiria para obter estabilidade lógica semelhante.

Em termos percentuais, a AWS afirma que a abordagem da Ocelot reduz a sobrecarga do qubit para correção de erros em até 90%. Esta é uma tremenda economia de recursos. A desvantagem é que o qubit lógico atual da Ocelot é apenas um único qubit – a correção de erros é usada para manter esse qubit estável, mas o chip ainda não executa lógica multi-qubit. Ainda assim, demonstrar um qubit lógico com 9 qubits físicos é um avanço na correção de erros. A taxa de erro lógico alcançada não foi explicitamente declarada, mas presumivelmente o qubit lógico tem uma vida útil dramaticamente maior do que qualquer transmon único. A AWS também implementou as primeiras portas lógicas de preservação de viés de ruído nos qubits cat. Essas são portas projetadas para não misturar erros X e Z (para que um erro de fase em um qubit cat não cause acidentalmente uma inversão de bits). Ao “desligar” certos canais de erro nas operações de porta, eles mantêm o viés de erro intacto mesmo durante os cálculos.

Em resumo, a estratégia de Ocelot é evitar a maioria dos erros e então corrigir o resto. Ao combinar o qubit cat (que inerentemente corrige inversões de bits) com um pequeno código externo para erros de fase, o qubit lógico de Ocelot pode operar em um regime onde o erro lógico por circuito é extremamente baixo – potencialmente baixo o suficiente para algoritmos práticos com muito menos qubits do que outras abordagens precisariam.

Microsoft Majorana-1

A abordagem da Microsoft é fazer qubits que sejam quase livres de erros no nível físico usando proteção topológica. Em teoria, um qubit topológico em um dispositivo Majorana perfeito teria zero erros de inversão de bits ou inversão de fase (além de erros não locais muito infrequentes). Na prática, Majorana-1 mostrou que muitos dos mecanismos de erro usuais estão ausentes – por exemplo, o qubit não é afetado por ruído local que perturbaria um qubit convencional. A única operação que não é protegida topologicamente é o chamado T-gate (umπ/4phase gate), que requer a introdução de um recurso não topológico (injeção de estado mágico). Isso significa que, embora os portões Clifford possam ser feitos essencialmente sem erro por meio de sequências de trança ou medição, o portão T terá algum erro que deve ser corrigido por meio de codificação de nível superior. O qubit Majorana, portanto, empurra a maior parte da sobrecarga de correção de erro para um nível muito alto (necessário apenas para lidar com esses portões T). O desempenho medido até agora: a leitura inicial do qubit teve um erro de ~1% por medição, que pode ser melhorado refinando o sensor de ponto quântico, e as inversões de paridade do qubit são ~10−3por ms, conforme mencionado. Se interpretarmos isso em um sentido de erro por operação, considere um qubit Majorana passando por uma sequência de operações, cada uma com ~1 µs de duração: em 1 µs, a chance de um erro espontâneo é ~10−6(já que 1 µs é 1/1000 de 1 ms T1). Essa é uma probabilidade de erro físico incrivelmente baixa, muito abaixo do limite típico (que é em torno de10−2).

Então, os qubits Majorana operam firmemente no regime abaixo do limite no nível de qubit único. O plano da Microsoft é alavancar isso construindo qubits lógicos que exigem muito menos qubits físicos. Eles estimam que um milhão de qubits Majorana físicos podem render na ordem de um milhão de qubits lógicos – essencialmente um físico por lógico, porque cada um já é (quase) um qubit perfeito. Na prática, alguma pequena sobrecarga será necessária para os T-gates: provavelmente eles implementarão uma correção de erro leve ou destilação apenas para essas operações. Mas a sobrecarga é constante, não enorme, porque todos os outros gates são protegidos. Este é um cenário qualitativamente diferente de, digamos, abordagens supercondutoras onde cada operação em cada qubit deve ser corrigida por redundância. A frase usada é que os qubits Majorana podem ser “quase livres de erros” em operação. O artigo da Nature da Microsoft demonstrou a existência e o controle desses qubits topológicos (um grande passo), e o roteiro de acompanhamento (no arXiv) descreve como passar do atual dispositivo de 8 qubits para uma máquina escalável e tolerante a falhas.

Em resumo, a filosofia de correção de erros da Microsoft é construir qubits que precisam de muito menos correção. Ao atingir taxas de erro físico bem abaixo do limite (paridade inverte ~10−6por operação), eles evitam a necessidade de grandes códigos quânticos para a maioria das operações. Eles ainda precisarão corrigir os erros raros (por exemplo, usando códigos de repetição para capturar quaisquer inversões de paridade que ocorram e usando fábricas de estados mágicos para T-gates), mas a sobrecarga de recursos é muito menor. É por isso que eles afirmam que seu chip poderia resolver problemas em escala industrial “ em anos, não décadas ” – porque se a física se mantiver, eles não terão que esperar por um milhão de qubits físicos apenas para obter 100 qubits lógicos; eles podem usar esses qubits físicos diretamente como qubits úteis.

Google Salgueiro

A abordagem do Google permanece dentro do paradigma convencional de qubit transmon, mas empurra as taxas de erro físico para baixo o suficiente para atingir o limite e, em seguida, usa códigos de correção de erro quântico padrão (QEC). No Willow, as taxas de erro de porta física são impressionantemente baixas: erro de qubit único ≈0,035% e erro de dois qubits ≈0,14% em média. Essas taxas de erro (aproximadamente3.5×10−4e1.4×10−3por porta, respectivamente) estão abaixo ou no mesmo nível do limite do código de superfície (~1% para um código de superfície padrão, potencialmente alguns décimos de um por cento para modelos de ruído mais realistas). Isso significa que os qubits do Willow são bons o suficiente para que adicionar redundância reduza os erros, não os amplifique. O Google demonstrou isso explicitamente: eles implementaram a correção de erro quântico no Willow e em um dispositivo menor de 72 qubits, alcançando resultados marcantes. Em um experimento recente, eles realizaram um código de superfície de distância 5 usando 72 qubits e um código de superfície de distância 7 usando 105 qubits (o Willow completo). A taxa de erro lógico do código de distância 7 foi significativamente menor do que a do código de distância 5, confirmando que a condição de limite foi atendida. Na verdade, o Google relatou que seu qubit lógico de distância 5 atingiu o “ponto de equilíbrio” – o que significa que a taxa de erro do qubit lógico foi quase igual à taxa de erro do melhor qubit físico, e o qubit lógico de distância 7 durou o dobro do tempo do melhor qubit físico no chip. Este é um marco histórico: é a primeira vez que um qubit lógico superou os componentes físicos em um dispositivo de estado sólido. Matematicamente, no código de superfície o erro lógicoplógicodeve ser dimensionado aproximadamente comoplógico≈UM(pfísicapdebulhar)(e+1)/2para grande distância de códigoe. O Google observou exatamente essa supressão exponencial: à medida que eles passavam da distância 3 para 5 e para 7, o erro lógico caía em linha com um erro por porta de ~0,1abaixo do limite. Eles também executaram códigos de repetição até a distância 29 (usando muitos qubits para um código linear simples) e viram o erro lógico diminuindo até que rajadas de erros correlacionados muito raros (como raios cósmicos) definiram um piso eventual em cerca de um erro por hora para o maior código. Esses eventos correlacionados (que causam erros simultâneos em muitos qubits) não são markovianos e não foram corrigidos pelo código; o Google mitigou alguns melhorando a fabricação de chips (engenharia de lacunas para reduzir picos de erro induzidos por radiação em 10.000× foi mencionada em um comentário). Para fontes de erro comuns, no entanto, o QEC de Willow funcionou como esperado.

O resultado é que o Google demonstrou uma operação tolerante a falhas em um protótipo: eles podem armazenar informações quânticas por mais tempo com um qubit lógico do que qualquer qubit individual pode contê-las. O erro lógico por ciclo em seu código de distância-7 foi de cerca de2.8×10−3, aproximadamente metade do erro físico do melhor qubit. À medida que eles melhoram ainda mais a fidelidade do qubit físico e escalam para códigos maiores (distância 11, etc.), o erro lógico diminuirá exponencialmente. O Google usa o código de superfície (um código topológico 2D) para esses experimentos, o que requer uma matriz 2D de qubits com portas vizinhas mais próximas – exatamente o que o Willow fornece. Eles também construíram um decodificador personalizado de alta velocidade para acompanhar o tempo de ciclo de escala de ~MHz do código. Em resumo, a técnica de correção de erros do Willow é a tradicional: codificar qubits lógicos em muitos qubits físicos (um código de superfície de distância 7 usou 49 qubits físicos) e executar medições de síndrome para corrigir erros em tempo real.

O importante é que Willow cruzou o limite: erro físico de dois qubits 0,14% < 1% significa que erros lógicos podem ser suprimidos exponencialmente. Então, diferentemente de dispositivos anteriores que eram “muito barulhentos para corrigir”, os qubits de Willow são bons o suficiente para se beneficiar do QEC. Isso abre o caminho para o dimensionamento – embora muito mais qubits sejam necessários para fazer algo como executar um algoritmo tolerante a falhas, o Google provou o conceito em hardware real.

IBM Heron R2

A IBM também vem reduzindo constantemente as taxas de erros físicos, embora na época da estreia do Heron R2, a IBM não tivesse mostrado publicamente um qubit lógico superando os qubits físicos. O erro de porta de dois qubits da IBM no Heron é de cerca de 0,3% (99,7% de fidelidade) em média, e os erros de qubit único são da ordem de 0,03% (99,97% de fidelidade). Esses são comparáveis aos números do Google, embora um erro de dois qubits ligeiramente maior. Isso coloca a IBM bem em torno do regime de limite também. A estratégia da IBM para correção de erros gira em torno do código de superfície no futuro, mas no curto prazo eles se concentraram na mitigação de erros e na “utilidade quântica” usando qubits não corrigidos. Como o Heron R2 pode executar circuitos com milhares de portas de dois qubits de forma confiável (consulte a seção Benchmarking), a IBM pode tentar algoritmos com profundidades rasas ou usar técnicas como extrapolação de ruído zero para mitigar erros em vez de corrigi-los completamente. Dito isso, o roteiro da IBM inclui explicitamente o escalonamento para computação quântica corrigida por erros. Eles têm desenvolvido o software e a infraestrutura clássica para QEC (por exemplo, decodificadores rápidos, bem como investigado variantes de rede hexagonal do código de superfície que mapeiam bem para layout de qubit hexadecimal pesado). A rede hexadecimal pesada é compatível com um código de superfície rotacionado, embora com alguns ajustes de limite devido à conectividade de grau 3. A IBM argumentou que o hexadecimal pesado na verdade reduz a sobrecarga para o código de superfície ao cortar o número de conexões que precisam ser gerenciadas, melhorando potencialmente o comportamento do limite ao reduzir erros correlacionados.

Os acopladores ajustáveis no Heron ajudam a suprimir erros de diafonia, o que significa que os erros são mais locais e estocásticos – uma suposição subjacente à maioria dos códigos QEC. Por exemplo, quando os qubits estão ociosos, os acopladores estão desligados, reduzindo muito o erro não intencional de dois qubits (que pode, de outra forma, criar erros correlacionados que são mais difíceis para o QEC lidar).

Além disso, a IBM introduziu “mitigação de sistema de dois níveis (TLS)” no R2, que aborda uma fonte de ruído específica (defeitos espúrios interagindo com qubits). Ao estabilizar o ambiente TLS, eles reduzem flutuações que poderiam fazer com que vários qubits errem ao mesmo tempo.

Esses avanços são cruciais para abordar o limite de tolerância a falhas com um chip grande. Embora a IBM não tenha anunciado uma demonstração de codificação lógica de nível de qubit como o Google fez, eles fizeram experimentos QEC menores no passado (por exemplo, em dispositivos de 5 qubits eles mostraram código de repetição e detecção de erro de código pequeno Bacon-Shor). Podemos esperar que a IBM tente um qubit lógico em um sistema maior em breve. Na visão da IBM, a correção de erros será integrada a uma arquitetura modular – eles falam sobre códigos concatenados ou conectar patches de código de superfície em vários chips no futuro. A IBM também frequentemente cita o número de que cerca de 1.000 qubits físicos por qubit lógico podem ser necessários para aplicações reais com códigos de superfície. As taxas de erro do Heron R2 (~0,3%) ainda estão um pouco acima do limite ideal, então a IBM provavelmente está almejando reduzir os erros para ~0,1% ou menos nas próximas gerações (com materiais aprimorados, conforme indicado por sua pesquisa em andamento). Enquanto isso, a IBM se apoia na mitigação de erros: por exemplo, eles usam mitigação de erros de leitura e cancelamento de erros probabilísticos em software para melhorar a fidelidade efetiva do circuito sem QEC completo. Isso permitiu que eles fizessem coisas como executar com sucesso circuitos com 5.000 portas de dois qubits e ainda obter resultados significativos. Esses resultados não são totalmente corrigidos de erros, mas sim mitigados. A diferença é que a mitigação não fornece supressão exponencial de erros com tamanho, mas pode estender o que é classicamente simulável ou melhorar a precisão para tarefas específicas. Então, pode-se dizer que a IBM está atravessando a linha — empurrando qubits físicos o mais longe possível e usando qualquer técnica de redução de erros disponível, até que seu hardware esteja bom o suficiente para justificar o salto para QEC completo. Dadas as fidelidades do Heron R2, a IBM está muito perto dessa linha.

Em resumo, a taxa de erro por gate da IBM está se aproximando do limite, e seu foco está na redução sistemática de erros (diafonia, vazamento, eventos correlacionados) para atender a todos os critérios de tolerância a falhas. Assim que cruzarem esse limite decisivamente, eles empregarão os códigos QEC padrão (provavelmente um código de superfície em hexadecimal pesado) para produzir qubits lógicos. Seus projetos e roteiro consideraram isso, garantindo que a arquitetura possa suportar ciclos rápidos de medição de síndrome e escalar logicamente. A IBM também menciona frequentemente operações quânticas tolerantes a falhas até 2026 como uma meta, o que implica que os sucessores do Heron (por exemplo, o Osprey de 433 qubits e o Condor de 1121 qubits e além) incorporarão o QEC.

USTC Zuchongzhi 3.0

A equipe da USTC ainda não relatou a construção de um qubit lógico; em vez disso, eles se concentraram em demonstrar a vantagem computacional quântica (uma tarefa ultradifícil para computadores clássicos). No entanto, as características de erro do Zuchongzhi 3.0 estão na mesma liga que o Google/IBM, o que significa que ele é, em princípio, capaz de executar códigos QEC. O erro médio de porta de dois qubits no Zuchongzhi 3.0 é de ~0,38% (um pouco maior que os 0,3% da IBM ou os 0,14% do Google) e o erro de um único qubit é de ~0,10%. Eles estão logo abaixo do limite de 1%. Ao melhorar um pouco mais essas fidelidades (o que pode vir da otimização contínua de materiais que eles descreveram), eles também podem tentar experimentos de código de superfície. Em seu artigo arXiv, os pesquisadores da USTC observam que aumentar a coerência do qubit e reduzir os erros de porta diretamente ” empurra os limites das capacidades atuais do hardware quântico ” e estabelece as bases para explorar a correção de erros em circuitos maiores. Notavelmente, mesmo sem a correção completa de erros, eles executaram uma mitigação de erros flexível durante a amostragem do circuito aleatório: eles redefiniram os qubits com frequência (por meio de medição e reinicialização) para evitar o acúmulo de erros e realizaram verificação estatística das saídas para garantir que os erros não estivessem dominando os resultados.

Para correção de erros propriamente dita, a USTC pode alavancar códigos similares aos do Google (já que sua rede é compatível com código de superfície também). Eles têm expertise em correção de erros quânticos do lado fotônico (o grupo de Pan demonstrou alguns códigos bosônicos com fótons). Não seria surpreendente se um próximo marco da USTC fosse um qubit lógico corrigido de erros também.

Uma nota interessante: a arquitetura do Zuchongzhi 3.0 com flip-chip pode ser benéfica para QEC porque o segundo chip pode incorporar circuitos para isolamento rápido de feedforward ou crosstalk necessário em ciclos de correção de erros. Além disso, seu uso de reset ativo de qubits (por meio de gates) entre rodadas é essencialmente parte de um ciclo de correção de erros (reset de qubits ancilla).

Em resumo, embora o Zuchongzhi 3.0 não tenha demonstrado um qubit lógico, suas taxas de erro físico (~0,1–0,4%) são baixas o suficiente para estarem à beira do limite de correção de erro. A prioridade da equipe até agora era alcançar um experimento de vantagem quântica, mas as mesmas melhorias de hardware (T1, T2 mais longos, melhores portas) se traduzem diretamente em habilitar computações corrigidas de erro em um futuro próximo. Dado que Willow e Zuchongzhi são tão semelhantes, podemos esperar que se o Google pode fazer QEC de distância 7, o dispositivo da USTC poderia replicar um feito semelhante com algum refinamento. Os pesquisadores declaram explicitamente que seus avanços em coerência e fidelidade “abrem caminhos para investigar como aumentos na contagem de qubit e na complexidade do circuito podem aumentar a eficiência na resolução de problemas do mundo real” – o que sugere a correção de erros como um desses caminhos para algoritmos do mundo real.

Resumo das taxas de erro e técnicas de correção de erros

Dois paradigmas complementares surgiram entre esses cinco: (1) Redução de erro intrínseco: AWS e Microsoft reduzem drasticamente as taxas de erro físico pelo design de qubit (qubits cat, qubits topológicos), visando minimizar a carga sobre os códigos de correção de erro. (2) Correção de erro ativa: Google, IBM e USTC melhoram seus qubits supercondutores para o regime de limite e, em seguida, aplicam códigos de correção de erro quântico (como o código de superfície) para suprimir ainda mais os erros. Ambas as abordagens estão correndo em direção ao mesmo objetivo de computação quântica tolerante a falhas. Uma desigualdade de condição de limite simplespfísica<pdebulharsustenta ambos – AWS/Microsoft satisfazem isso ao fazerpfísicaextremamente pequeno para certos erros, e o Google/IBM/USTC satisfazem isso por engenhariapfísicaabaixo do conhecidopdebulhar∼1para códigos de superfície. Em última análise, todos os cinco esforços visam realizar qubits lógicos com taxas de erro baixas o suficiente para circuitos quânticos profundos e confiáveis. Já vemos Ocelot alcançando um qubit lógico funcional com uma redução de recursos de 85%, e Willow demonstrando uma memória lógica que supera qualquer qubit físico único. Essas são fortes validações de que a correção de erros – seja intensiva em hardware ou software – está prestes a tornar a computação quântica escalável.

Benchmarking e Métricas de Desempenho

Para comparar processadores quânticos, uma variedade de benchmarks e métricas são usados, desde métricas independentes de dispositivo como Quantum Volume até benchmarks específicos de tarefa como amostragem aleatória de circuitos. Consideraremos algumas medidas-chave de desempenho: volume quântico (QV), Circuit Layer Operations Per Second (CLOPS), benchmarking algorítmico (experimentos de vantagem quântica) e outros números de desempenho publicados como escalonamento de fidelidade em grandes circuitos.

Volume quântico

QV é uma métrica holística introduzida pela IBM que considera o número de qubits, a fidelidade do gate e a conectividade, encontrando o maior circuito aleatório de largura e profundidade iguais que o computador pode implementar com uma probabilidade de sucesso > 2/3. Um QV mais alto (que normalmente é relatado como2epara algum inteiroe) significa que a máquina pode lidar com circuitos emaranhados maiores de forma confiável.

IBM Heron R2

Entre nossos cinco chips, o IBM Heron R2 tem atualmente o maior QV relatado. A IBM anunciou que o Heron atingiu Quantum Volume = 512 (já que um Eagle de 127 qubits hexadecimais pesados atingiu QV 128 antes, a melhor fidelidade do Heron o empurrou para 512). QV 512 corresponde à execução bem-sucedida de um circuito aleatório de 9 qubits de profundidade 9 (já que29=512). Isso indica que Heron pode emaranhar pelo menos 9 qubits profundamente com boa fidelidade.

Google Willow e USTC Zuchongzhi 3.0

Nem o Google nem a USTC relataram formalmente o QV para Willow ou Zuchongzhi, mas, dadas suas especificações, pode-se inferir. Willow com 105 qubits e 99,86% de fidelidade de dois qubits provavelmente poderia atingir um QV semelhante ou maior (talvez 512 ou 1024) se medido, porque tem ainda mais qubits para negociar pela profundidade do circuito. O Google normalmente se concentra em marcos específicos em vez de QV, mas as capacidades demonstradas (como um circuito aleatório completo de 105 qubits em profundidade > 30 no experimento de vantagem) excedem em muito o que o QV 512 implica. Na verdade, o QV se torna menos informativo na vanguarda, onde os benchmarks direcionados são mais ilustrativos (por exemplo, o Google pode dizer que seu volume quântico é efetivamente ilimitado para tarefas de amostragem aleatória, uma vez que eles superam o clássico por uma margem enorme).

AWS Jaguatirica

O QV do AWS Ocelot não é diretamente aplicável, pois atualmente ele realiza um qubit lógico – QV é definido para circuitos, então um único qubit lógico não pode gerar um circuito multi-qubit emaranhado. O conceito de QV se aplicará ao Ocelot somente quando ele for dimensionado para múltiplos qubits lógicos que podem executar um circuito não trivial. No entanto, pode-se considerar a vida útil ou a taxa de erro do qubit lógico como medidas de desempenho análogas (discutidas acima).

Microsoft Majorana-1

O QV do Microsoft Majorana-1 também ainda não é significativo – com 8 qubits físicos que estão em estágios experimentais iniciais, eles não executaram circuitos aleatórios. O propósito do Majorana-1 não é maximizar o QV neste estágio, mas validar o novo tipo de qubit. Então, em termos de QV: a IBM lidera com 512, e o Google/USTC provavelmente tem capacidades de circuito efetivas comparáveis ou maiores, embora não o enquadrem em termos de QV. Vale a pena notar que outra empresa, a IonQ, reivindicou QVs muito altos (por exemplo, 2.097.152), mas isso é para sistemas de íons presos com menor velocidade de gate; nosso foco está nesses cinco chips. Entre esses cinco, o QV 512 do Heron R2 é uma referência concreta de sua contagem e fidelidade de qubits balanceados.

CLOPS (Operações de Camada de Circuito por Segundo)

Esta métrica definida pela IBM mede quantas camadas de um circuito parametrizado o sistema pode executar por segundo (incluindo overheads de compilação e feedback). Ela mede o throughput ou a velocidade de execução de circuitos quânticos.

IBM Heron R2